# Simultaneous optimization of the area, wirelength and TSVs in a 3D IC design

# Atul Prakash<sup>1</sup>, Rajesh Kumar Lal<sup>2</sup>

<sup>1,2</sup>Department of Electronics & Communication Engineering, Birla Institute of Technology, Ranchi 835215, India.

E-mail: <sup>1</sup>prakashatul.uit@gmail.com; <sup>2</sup>rklal@bitmesra.ac.in

**Abstract:** The technology of a three-dimensional integrated circuit (3D-IC) is an emerging approach for improving performance. In comparison to a standard 2-D IC design, which arranges all of the devices on a single planar layer, a 3D-IC stacking of many tiers enables more devices to be placed close together, resulting in the significant area and wirelength reduction. Designing a 3D-IC introduces an extra parameter to be considered while assigning a layer to any circuit component where different layers are connected by Through Silicon Vias. In this paper, we have applied the Parallel-PSO approach to optimize the area, wirelength of the layout and the number of TSVs to connect the different layers simultaneously. The results are obtained and compared with the benchmark circuits available with MCNC and GSRC.

**Keywords:** Sequence pair (SP), Very large scale integrated circuit (VLSI), 3D-IC, TSVs PSO, Floorplanning, MCNC, GSRC

#### 1 Introduction

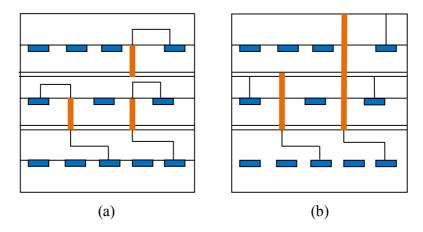

A three-dimensional IC is an Integrated circuit manufactured by laying several vertical silicon wafers or die. The different layers are connected either by Through Silicon Vias (TSVs) or by Cu-Cu interconnects [1-5]. While the Cu-Cu interconnection with silicon generates sheer force between them, there is a high chance of failure when IC is heated and hence TSVs are widely used to connect these different layers. Recently 3-D integration has attracted researchers as it provides a higher device density as well as higher bandwidth. It is also possible to integrate heterogeneous technologies in a layered die stack structure, which counteracts system-on-chip integration. Other benefits of 3-D ICs include smaller footprints; lower interconnect delays, higher performance, as well as lower power consumption. 3-D IC changes the wirelength distribution from 2-D layout. Nets can be made shorter in 3-D layout, but TSVs are not free and therefore cannot be used at random. There are two approaches used to design 3-D ICs, via-first and via-last. The TSVs in the Via-first approach only interfere with the device layers [Fig: 1(a)], while in the Via-Last approach: the TSVs interact not only with the device layers but also with the metal layers [Fig: 1(b)].

Figure 1: (a) Via-First TSVs & (b) Via-Last TSVs [6]

The inputs to 3D-ICs are:

- 1. A set of blocks with a specific shape and size,

- 2. A list of number of terminals on each block and,

- 3. The netlist describing the interconnections between these blocks.

#### 2 Problem Formulation

We have focused our work in Two-Layer/Four-Layer 3D-IC, where we have partitioned the set of blocks in two/four different layers such that their area difference is as small as possible.

Let  $B = \{b_1, b_2, \dots, b_n\}$  be a set of 'n' modules. The module  $b_i$  could be represented by  $(W_i, H_i)$ ,  $1 \le i \le n$ , where  $W_i$  is its width and  $H_i$  is its height.

Let  $\eta = \{N_1, N_2, \dots, N_m\}$  be the set nets, where 'm' denotes the total number of nets that link the blocks,

Taking  $L_i$  as the estimated length of net  $N_i, 1 \le i \le m$ , The placement objective is to identify a group of rectangles represented by  $R = \{r_1, r_2, \dots, r_n\}$  for each block represented by set B such that,

- 1. Each block  $b_i$  can be placed either in the two layer

- 2. Each  $b_i$  block can be put in the rectangle  $r_i$ , which has the dimensions  $(W_i, H_i)$ .

- 3. No two modules overlap each other, that is  $r_i \cap r_j = \Phi$ ,  $1 \le i, j \le n$ .

- 4. The total area occupied by *R* is minimized

5. The total wirelength determined by Σ<sup>m</sup><sub>i=1</sub> L<sub>i</sub>, is minimized.

6. The total number of TSVs should be minimized.

## 2.1 Area Optimization

VLSI floorplanning consists solely of the arrangement of non-overlapping rectangles. The arrangement of blocks on a chip is divided into two types: slicing floorplan and non-slicing floorplan. The sequence-pair (SP) approach was used to investigate the non-slicing floorplan in this work. Sequence pair is a technique for packing bocks that use a pair of modules known as sequences. The ability to have a limited solution space is essential for successful optimization. Murata et. al. [7] has demonstrated that the SP's searching space results in an effective rectangular packing of the modules.

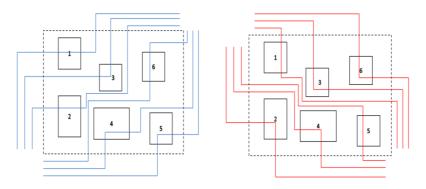

Tang et.al. [8] Proposed a method called Fast Longest Common Subsequence (fast LCS) to encode a sequence pair to its corresponding floorplan. The first order of sequence-pair  $S_1$ ) is formed by arranging the lines drawn from the chip's southwest corner to its northeast corner in a linear fashion. These are non-intersecting, non-overlapping lines that each pass through one module. The second-order sequence pair  $(S_2)$  is obtained by drawing similar lines from the chip's southeast corner to its northwest corner.

Fast LCS is a quick and easy way to calculate LCS for a given sequence pair, where n represents the number of items and the weights is not limited to 1 or integers like LCS.

Figure 2: The sequence-pair for the specified placement is (132645, 245136)

If the blocks are 1,2,3...n and the input sequence pair is  $(S_1, S_2)$ , then both  $S_1$  and  $S_2$  are permutations of  $\{1,2,...n\}$ . The array P(b), b=1,2,...,n of block positions is used to store the coordinates of block b based on the their weight vector w(b), which corresponds to the width or height of block b. The array match(b), b = 1, 2, ..., nbe  $match[b].x = iandmatch[b].y = j if b = S_1[i] = S_2[j],$ the length  $L[1,2,3,\ldots,n]$  represents the length of candidates for the longest common subsequence. The following is the algorithm:

## Pseudo code of Fast LCS [8]

- 1. Initialize Match Array match

- 2. Initialize Length Array L with 0

- 3. **for** i = 1 to n

- 4. **do**  $b = S_1[i]$

- 5. P = match[b].y;

- 6. P[b] = L[p];

- 7. t = p[b] + w(b);

- 8. for j = P to n

- 9. **do** if(t > L[j])

- 10. **then** L[j] = t;

- 11. else break;

- 12. return L[n]

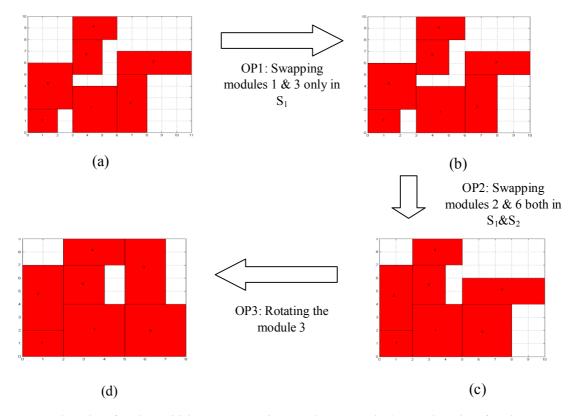

There are three distinct sorts of procedures that may be used to transform a sequence pair to another, which are as follows:

- Op1: Swap the names of two modules in any of the two sequences.

- Op2: Swap the names of two modules in each sequence.

- Op3: Rotate a module as the third option.

To demonstrate the impact of a perturbation on a sequence pair, consider an example with seven modules of dimension as (3,4), (2,5), (5,2), (3,2), (2,3), (3,4), (2,2) and the initial sequence pair  $(S_1, S_2)$  as (6475312,7612534).

**Figure 3:** A Floorplan for the Initial sequence pair (6475312,7612534). **b** Floorplan for the sequence pair (6475132,7612534) (after exchanging module 1 & 3 only in Sequence  $S_1$ ). **c** Floorplan for the sequence-pair (2475136,7216534) (After exchanging module 2 and 6 in both Sequences  $S_1$  &  $S_2$ . **d** Floorplan for the sequence pair (2475136,7216534), when module 3 is rotated

Figure numbers 3 shows the effect of these operations. The floorplan's dimensions change from  $11 \times 10$  to  $10 \times 10$  to  $10 \times 9$  to  $8 \times 9$  respectively. This example demonstrates how allowing these three valid operations on a sequence pair can significantly alter the floorplan area.

# 2.2 TSVs Optimization

The 3D-IC design problem involves division of the circuit netlist into multiple parts (in our case two or four parts) such that there are some connections between these parts. The number of edges in the two parts of the circuit is the number of TSVs in the 3D-IC and this number can be calculated as follows:

$$T = \sum_{i=1}^{k} \sum_{j=1}^{k} T_{ij} , (i \neq j)$$

Where  $i, j$  are the edge's vertices. (1)

T = total number of TSVs

$$T_{ij} = \begin{cases} 1, & \text{if } i^{th} \text{ node in bottom laye has a connection with } j^{th} \text{ node of top layer} \\ 0, otherwise \end{cases}$$

The design problem in first stage is a partitioning problem where the netlist, say V is to partition into  $V_1 \& V_2$ , such

$$V_1 \cap V_2 = \emptyset$$

And,

$$V_1 \cup V_2 = V$$

(3)

$$V_1 \cup V_2 = V \tag{3}$$

As the problem involves bipartitioning of a circuit, so equality condition must be satisfied as

Number of nodes in partition

$$1 \cong number$$

of nodes in partition  $2$  (4)

## 2.3 Wirelength Estimation

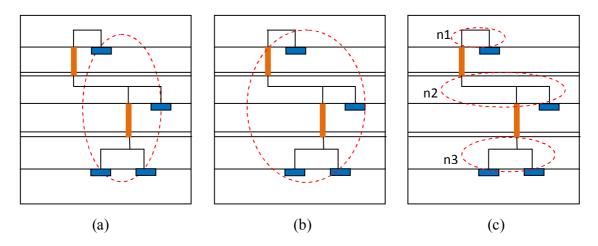

In 3-D floorplanning, there is a high chance that all the terminals of a net may lie in multiple layers and hence the lateral wirelength calculation becomes necessary. Most of the works related to the calculation of lateral wirelength suggested using Half Perimeter Wirelength (HPWL), Wirelength of a net is determined by measuring half perimeter of the bounding box of all its terminals, assuming they are all in the same plane, as shown in figure 6.2 (a) [9].

Figure 6.2: wirelength estimation models (a) Bounding box of all terminals of a net, (b) Bounding box of all terminals of a net and TSVs associated with them and (c) a net divided into subnets and summing up individual subnet wirelength

The drawback of this method is that it estimates the lateral wirelength without any information of TSVs locations. Although this is unavoidable as the floorplan do not take care of the TSV placements. In the other technique to estimate the wirelength, the bounding box is chosen such that it covers all the terminals of the net as well as the TSVs associated with that net as illustrated in figure 6.2(b). However, it underestimates the total wirelength when a net has terminals in multiple dies [9].

To overcome the drawbacks of these two methods, in our technique we have estimated the total lateral wirelength by first calculating wirelength on each individual dies then summing up them. Also in our proposed technique, the wirelength of a net (say n) on a particular die is calculated by the half perimeter wirelength of all its terminals on that die and any TSV of n in the same die or die above/below it. In figure 6.2(c), the lateral wirelength of a 3D net n is obtained by summing up the estimated wirelength of subsets n1, n2 & n3 [10].

Here we have bipartitioned the netlist hence the total wirelength will be calculated as the sum of wirelength of partition  $0(W_0)$ , wirelength of partition  $1(W_1)$  and the wirelength due to TSVs  $(W_T)$ ,

Hence total wirelength

$$L = W_0 + W_1 + W_T$$

(5)

To estimate the wirelength due to TSVs we have taken the TSV size as 3  $\mu$ m as in [9093] unless otherwise specified.

Hence,  $W_T = T \times 3 \,\mu m$  (6) Where, T is the total number of TSVs The TSV size is  $3 \,\mu m$  as in [5] unless otherwise specified.

## 2.4 Combined Area, Wirelength and TSVs optimization

While the purpose of traditional 3D-IC design methods is to reduce the number of TSVs, integrating it with the area and wirelength reduction makes this work much harder. Designing multi-objective 3D-ICs is substantially more complicated. One of the most challenging aspects of multi-objective optimization is that there is no one best solution for every target in the solution space. Additionally, adopting an ideal solution for one goal may necessitate receiving a suboptimal result for another. Hence, it is difficult to define what constitutes a good answer. The formulation of a good solution is adopted as it appears in [11]:

- 1. Allow for more precise handling of the tradeoffs between goals.

- 2. Produce partitioning that is predictable.

- 3. Provide a method for dealing with objectives that correspond to amounts of various types.

In this case, a design technique is required that can optimize objective T, the number of TSVs, minimization of objective A, the total area occupied by the modules in two/four-layer and minimizing objective W, the total wirelength. However, the three objectives are dissimilar objectives, which means that optimizing T alone does not necessarily imply that A and W are optimized and vice-versa. That is why we adopt a combination-based formulation for multi-objective optimization: The combined objective will be a scalar combined metric  $C^c$  given by the following equation:

$$C^{c} = \lambda * \frac{A}{norm(A)} + (1 - \lambda) * \frac{W}{norm(W)} + T$$

(7)

Where,

$C^c = Combined \ objective \ function,$   $\lambda = weight \ given \ to \ area (0 \le \lambda \le 1)$  ,  $A = Total \ area \ occupied \ by \ the \ modules \ in \ different \ layers \ of \ 3D \ IC$   $L = Total \ wirelength \ of \ 3D \ IC$   $T = Total \ numbers \ of \ TSVs$   $norm(A) = normalized \ area$   $norm(L) = normalized \ wirelength$

Minimizing equation (1) seeks to calculate a 3D layout that is as close as possible to any of the best in terms of any beginning goal. The area weight may be used to traverse the distance between each objective's best solution locations, resulting in a predictable structure based on the area weight as well as fine-tuned management of the tradeoff between the three objectives.

#### 3. The 3D-IC design technique

In the present work, a P-PSO algorithm [12] for the optimization of multimodal continuous functions is proposed. P-PSO is used for global optimization by updating particle locations to achieve quick convergence. To determine the layout in each of the two layers the sequence pair (SP) technique with LCS as described in chapter 4 has been used. Firstly, the given netlist has been bi-partitioned and then four different types of operations are allowed to perturb the bi-partitioned circuit and in the given sequence pair to another sequence pair listed as:

- Op1: Swap two module names in all the partitions.

- Op2: Swap two module names in only one sequence of each partition.

- Op2: Swap two module names in both sequences of each partition.

- Op3: Rotate a module in each partition.

To start with the designing of 3D-IC we first converted the information provided by the netlist into a matrix known as *adjacency matrix*, where column and row represents the nodes. Then we ha randomly bipartition the given netlist by calling the *initial\_position* function. In the next step the total number of interconnections (TSVs) between different layers of 3D-IC is calculated. Total area (A) occupied along with the amount of wirelength required to connect different nodes are calculated. The combined objective function as given in equation 6.5 in initiated. The proposed parallel Particle Swarm Optimization is then applied to achieve the minimum of all the three parameters viz. Area, Number of TSVs and the Wirelength requirement. The steps for the proposed approach for the 3D design problem under consideration are presented as under:

# Algorithm for 3D IC design using P-PSO

- 1. Start at the beginning of netlist and convert it into matrix form.

- 2. Bipartition the circuit into 0 and 1 partitions as

$$\sum_{i=0}^{L} l_i = \sum_{i=0}^{k} m_i + \sum_{j=0}^{k} n_j$$

(total number of nodes (l<sub>i</sub>)

Also, from (4),

Number of nodes in partition  $1 \cong$  number of nodes in partition 2 where  $l_i = m_i + n_i$

3. Calculate their TSV using

TSVs between partitions

$$(T_{ij}) = \sum_{i=0}^{k} m_i (\sum_{j=0}^{k} n_j)$$

(9)

4. Determine the position of modules in each partition and determine the corresponding area and wirelength using Sequence pair (SP) technique with the help of LCS. The total area and wirelength are as:

$$A = A_0 + A_1$$

$$L = W_0 + W_1 + W_T$$

(10)

(11)

Where

$A_0 = Area \ of \ Partition \ 0$

$A_1 = Area of Partition 1$

$W_0 = wirelength \ of \ Partition \ 0$

$W_1 = wirelength of Partition 1$ , and

$W_T$  = wirelength due to TSVs

- 5. Initialize the two different sets of PSO parameters parallelly with the same number of particles corresponding to each node of the sequence pair

- NP, w1, w2,  $iter_{max}$ , c1i, c1f, c2i, and c2f( $NP = number\ of\ particles$ )

- 6. Correspondingly evaluate fitness function,  $C_{ij}$ , for all the particles using (6.5), taking weight  $\lambda = 0.5$ , (for 50% weight to Area and Wirelength objectives).

- 7. Randomly initialize position vector of each pair of particles  $x_{ij}$  (i = 1,2,...NP & j = 1,2)

- 8. Generate initial velocity vector  $v_{ij}$  (i = 1, 2, ..., NP & j = 1, 2) for each pair of particles

- 9. evaluate the fitness value of each pair of particles using the objective function (using equation 5)

- 10. set *pbest* and *gbest* in the swarm for both pair of particles

- 11. **while** iteration < iter<sub>max</sub>

- 12. update the inertia weight

$$w = (w_1 - w_2) \times \frac{(iter_{max} - iter)}{iter_{max}} + w_2$$

13. update  $C_1 \& C_2$

$$C_1 = \left(C_{1f} - C_{1i}\right) \times \frac{iter}{iter_{max}} + C_{1i}$$

$$C_2 = \left(C_{2f} - C_{2i}\right) \times \frac{iter}{iter_{max}} + C_{2i}$$

14.  $for \ i = 1: NP$

15.  $for \ j = 1: 2$

16. update the velocity vector  $v_{ij}$

$$v_{id} = w \times v_{ij} + C_1 \times r_1^d \times \left(pbest_{ij} - x_{ij}\right) + C_2 \times r_2^d \times \left(gbest_{ij} - x_{ij}\right)$$

17. update the position vector  $x_{ij}$

$$x_{ij} = v_{ij} + x_{ij}$$

18.  $do$

Op1: Swap two module names corresponding to  $x_{i1} \& x_{i2}$  in both the partition

Op1: Swap two module names corresponding to  $x_{i1} & x_{i2}$  in both the partitions and calculate the fitness function as f1.

Op1: Swap the positions of the modules corresponding to  $x_{i1}$ &  $x_{i2}$  in  $S_1$  and calculate the fitness function as f2.

Op2: Swap the positions of the modules corresponding to  $x_{i1}$  &  $x_{i2}$  in both the sequence  $S_1 \& S_2$  and calculate the fitness function as f3.

Op3: Rotate the modules corresponding to  $x_{i1}$ &  $x_{i2}$  and calculate the fitness function as f4 Chose the best fitness among  $f_1$ ,  $f_2$ ,  $f_3 \& f_4$

19.  $if x_{ij}$  is better than the pbest<sub>ij</sub> Update  $pbest_{ij} = x_{ij}$

20. end if

21. if  $x_{ij}$  is better than the  $gbest_{ij}$ Update  $gbest_{ij} = x_{ij}$

22. end if

23. end for i

24. end for i

25. iteration = iteration + 1

26. end while

# 4. Parameters of the proposed algorithm

The values of the parameter  $C_{1i}$ ,  $C_{1f}$ ,  $C_{2i}$ ,  $C_{2f}$ ,  $w_1 \& w_2$  are crucial since it ensures that the suggested PSO algorithm balances exploration and exploitation.  $C_1$  is a cognitive parameter that highlights personal best performance while the social parameter  $C_2$  prioritizes the global best. Despite the lack of a well-defined procedure for selecting these numbers, several scholars have underlined the importance of maintaining  $C_1$  and  $C_2$  values so that  $C_1 + C_2 = 4$ , in which a good outcome is obtained in a different environment. To keep the total of cognitive and social factors at 4, we experimented with setting the values of  $C_{1i}$ ,  $C_{1f}$ ,  $C_{2i}$ , &  $C_{2f}$  to 0.5, 3.5, 3.5 & 0.5 respectively, which resulted in an improved solution. A linearly varying inertial weight of 0.1 to 1 is used. A smaller inertia weight value prioritizes the search in the local best's neighborhood, whereas a larger value global best promotes the search globally. As a result, early on in the process, local search is strong and as the operation progresses, global search becomes more sophisticated.

## 5. Experimental Results

We simulated the proposed 3-D floorplans with are, wirelength & TSV co-optimization. We used the MCNC & GSRC hard benchmark suites as our test cases. We have the unit in the MCNC & GSRC benchmarks to 1 µm. The TSV size is 3 µm as in [5] unless otherwise specified. The IO pad locations are assigned randomly. First, we tested our approach for two-layered 3D-IC then for a fair comparison the four-layered results were obtained and compared with [13, 5 and 9]; the comparison results are shown in table 6.1. The Tabu Search and Simulated Annealing techniques were used and designed to optimize the area and TSVs by [13]. In [5] authors applied the shuffling frog leaping method to tackle the optimization issue of 3D IC design in terms of area and TSVs count. SA [9] was used by to optimize the wirelength and TSVs. They presented their technique in two stages, stage one planned the hard macros and TSV-blocks at the same time. The wirelength is improved in stage two by reassigning signal TSVs. Further in Table 6.2 and Table 6.3 we have presented the optimization results of Area, Wirelength and TSVs simultaneously for two layered 3D IC design for MCNC and GSRC Benchmarks respectively.

**Table 1:** Characteristics of MCNC Benchmark circuits

| Circuit | Modules | Nets | I/O Pads | Pins | Area(mm <sup>2</sup> ) |

|---------|---------|------|----------|------|------------------------|

| ami33   | 33      | 123  | 42       | 522  | 1.1564                 |

| ami49   | 49      | 408  | 22       | 953  | 35.4454                |

Table 2: Characteristics of GSRC Benchmark circuits

| Circuit | Modules | Nets | Pins | Area(mm <sup>2</sup> ) |

|---------|---------|------|------|------------------------|

| n50     | 50      | 485  | 1050 | 182962                 |

| n100    | 100     | 885  | 1873 | 179501                 |

| n200    | 200     | 1583 | 3599 | 175696                 |

| n300    | 300     | 1893 | 4358 | 273170                 |

Table 3: 4-layered 3D IC Parameters optimization comparison of results on MCNC & GSRC Benchmark Circuits

| Benchmar<br>  k | Algorithm         | Tabu<br>Search<br>[13] | SFLP [5] | SA [9] | ours    | % improve- ment over [13] | %<br>improve-<br>ment over<br>[9] |

|-----------------|-------------------|------------------------|----------|--------|---------|---------------------------|-----------------------------------|

| ami33           | WL(μm)            |                        |          | 45179  | 28750   |                           | 36.36                             |

|                 | Avg.<br>Area(μm²) | 573000                 | 586000   |        | 339136  | 40.81                     |                                   |

|                 | TSV               | 116                    | 108      | 141    | 159     | -37.07                    | -12.76                            |

|                 | WL(μm)            |                        |          | 585804 | 365666  |                           | 37.58                             |

| ami49           | Avg.<br>Area(μm²) | 7481931                | 7481895  |        | 9167900 | -22.53                    |                                   |

|                 | TSV               | 292                    | 263      | 436    | 171     | 41.44                     | 60.78                             |

|                 | WL(µm)            |                        |          |        | 17906   |                           |                                   |

| n30             | Avg.<br>Area(μm²) |                        |          |        | 55025   |                           |                                   |

|                 | TSV               |                        |          |        | 310     |                           |                                   |

|                 | WL(μm)            |                        |          |        | 24628   |                           |                                   |

| n50             | Avg.<br>Area(μm²) |                        |          |        | 51622   |                           |                                   |

|                 | TSV               |                        |          |        | 446     |                           |                                   |

|                 | WL(μm)            |                        |          | 148748 | 53514   |                           | 64.02                             |

| n100            | Avg.<br>Area(μm²) | 48170                  | 48112    |        | 45087   | 6.40                      |                                   |

|                 | TSV               | 996                    | 804      | 1171   | 742     | 25.50                     | 36.64                             |

| n200            | WL(μm)            |                        |          | 291091 | 99728   |                           | 65.74                             |

|                 | Avg.<br>Area(μm²) | 50646                  | 51097    |        | 45971   | 9.23                      |                                   |

|                 | TSV               | 2035                   | 1468     | 2179   | 1542    | 24.23                     | 29.23                             |

| n300            | WL(µm)            |                        |          | 391694 | 164364  |                           | 58.04                             |

|                 | Avg.<br>Area(μm²) | 76223                  | 76478    |        | 71751   | 5.87                      |                                   |

|                 | TSV               | 2133                   | 1823     | 2730   | 1793    | 15.94                     | 34.32                             |

**Table: 4:** 2-layered 3D IC Parameters optimization results for MCNC Benchmark Circuits

| Benchmark | Benchmark Parameters      |          |

|-----------|---------------------------|----------|

|           | Wirelength (µm)           | 20668    |

| Apte      | Avg.<br>Area(μm²)         | 53191804 |

|           | TSV                       | 9        |

|           | Wirelength (µm)           | 205399   |

| Xerox     | Avg.<br>Area( $\mu m^2$ ) | 19701250 |

|           | TSV                       | 18       |

|           | Wirelength (µm)           | 84308    |

| Нр        | Avg.<br>Area( $\mu m^2$ ) | 8930936  |

|           | TSV                       | 6        |

|           | Wirelength (µm)           | 64992    |

| ami33     | Avg.<br>Area(μm²)         | 1164240  |

|           | TSV                       | 42       |

|           | Wirelength (µm)           | 36812916 |

| ami49     | Avg.<br>Area( $\mu m^2$ ) | 768986   |

|           | TSV                       | 98       |

**Table 5:**2-layered 3D IC Parameters optimization results for GSRC Benchmark Circuits

| h                  |                   |        |  |

|--------------------|-------------------|--------|--|

| <b>Benchmark ▼</b> | <b>Parameters</b> | Result |  |

|                    | Wirelength        | 15528  |  |

|                    | $(\mu m)$         | 13328  |  |

| n10                | Avg.              | 230468 |  |

|                    | Area( $\mu m^2$ ) |        |  |

|                    | TSV               | 12     |  |

|                    | Wirelength        | 54914  |  |

|                    | $(\mu m)$         | 31911  |  |

| n30                | Avg.              | 221028 |  |

|                    | Area( $\mu m^2$ ) |        |  |

|                    | TSV               | 57     |  |

|                    | Wirelength        | 90182  |  |

|                    | $(\mu m)$         | 70102  |  |

| n50                | Avg.              | 207208 |  |

|                    | Area( $\mu m^2$ ) |        |  |

|                    | TSV               | 127    |  |

|                    | Wirelength        | 156698 |  |

| 400                | (μm)              | 120070 |  |

| n100               | Avg.              | 176599 |  |

|                    | Area(µm²)         |        |  |

|                    | TSV               | 251    |  |

|                    | Wirelength        | 270722 |  |

| 200                | (μm)              |        |  |

| n200               | Avg.              | 185008 |  |

|                    | Area(µm²)         | 40.5   |  |

|                    | TSV               | 485    |  |

|                    | Wirelength        | 429918 |  |

| 200                | (μm)              |        |  |

| n300               | Avg.              | 292008 |  |

|                    | Area(μm²)         |        |  |

|                    | TSV               | 639    |  |

Table 6: Runtime (in seconds) comparison for 4-Layered 3D IC

| Benchmark | Runtime<br>(in seconds)<br>SA [9] | Runtime<br>(in seconds)<br>(Proposed-PSO) | %<br>Improvement |

|-----------|-----------------------------------|-------------------------------------------|------------------|

| ami33     | 42.46                             | 63.15                                     | -48.73           |

| ami49     | 184.63                            | 126.33                                    | 31.58            |

| n30       |                                   | 61.52                                     |                  |

| n50       |                                   | 114.35                                    |                  |

| n100      | 1306.39                           | 306.65                                    | 76.53            |

| n200      | 8237.10                           | 1422.19                                   | 82.73            |

| n300      | 21450.50                          | 2793.42                                   | 86.98            |

**Table 7:** Runtime for 2-Layered 3D IC (in seconds)

| Benchmark | Runtime<br>(in seconds)<br>(Proposed-PSO) |  |

|-----------|-------------------------------------------|--|

| apte      | 7.58                                      |  |

| xerox     | 8.59                                      |  |

| hp        | 6.95                                      |  |

| ami33     | 21.62                                     |  |

| ami49     | 39.23                                     |  |

| n10       | 4.29                                      |  |

| n30       | 20.57                                     |  |

| n50       | 36.54                                     |  |

| n100      | 79.65                                     |  |

| n200      | 396.12                                    |  |

| n300      | 598.95                                    |  |

#### 6. Summary

3D integrated circuits (3D-ICs) are a new technology that has a lot of promise. 3D-ICs have a tiny footprint and vertical linkages between dies, allowing for shorter wirelength between gates. As a result, they have lower connection latency and power consumption. The 3D Partitioning and Layer Assignment stage is the first of several in the design flow of 3D integrated circuits. This step is crucial since the outcome will have an impact on the performance of succeeding processes. This issue is NP-hard, much like other partitioning problems. The

implementation of iterative heuristics [14] was used to handle this essential problem. When attempting to tackle this problem, several factors have been considered. Layer assignment, TSV reduction, wirelength optimization and area balance are some of these considerations. To do this objective, we have proposed Parallel PSO (P-PSO). The result obtained were compared and found to be giving better solutions when compared to other algorithms. As shown in table 3 as compared to SA [9] the average wirelength has an average improvement of 52.35% and the TSV count has an average improvement of 29.64%. Our results show an average improvement of 8.36% over the area occupied by the three-layered 3D IC and an average improvement of 14% over TSV count as compared to the results with Tabu Search [14].

## References

- [1] M. Jung, T. Song, Y. Peng and S. K. Lim, "Design Methodologies for Low-Power 3-D ICs With Advanced Tier Partitioning," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 25, no. 7, pp. 2109-2117, 2017.

- [2] J. Lin and J. Yang, "Routability-Driven TSV-Aware Floorplanning Methodology for Fixed-Outline 3-D ICs," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 36, no. 11, pp. 1856-1868, 2017.

- [3] W. Liu, Y. Wang, G. Chen, Y. Ma, Y. Xie and H. Yang, "Whitespace-Aware TSV Arrangement in 3-D Clock Tree Synthesis," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 9, pp. 1842-1853. 2015.

- [4] T. Song, S. Panth, Y. Chae and S. K. Lim, "More Power Reduction With 3-Tier Logic-on-Logic 3-D ICs," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 35, no. 12, pp. 2056-2067, 2016.

- [5] J. Kadambarajan and S. Pothiraj, "TSV Aware 3D IC Partitioning with Area Optimization," *Arabian Journal for Science and Engineering (online)*, 2021.

- [6] S. Banerjee, A. Ratna and S. Roy, "Satisfiability modulo theory based methodology for floorplanning in VLSI circuits," in proc. *Sixth International Symposium on Embedded Computing and System Design (ISED)*, Patna, India, pp. 91-95, Dec. 2016.

- [7] H. Murata, K. Fujiyoshi, S. Nakatake and Y. Kajitani, "VLSI module placement based on rectangle-packing by the sequence-pair," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 15, no. 12, pp. 1518-1524, 1996.

- [8] Xiaoping Tang, Ruiqi Tian and D. F. Wong, "Fast evaluation of sequence pair in block placement by longest common subsequence computation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 20, no. 12, pp. 1406-1413, 2001.

- [9] M. Tsai, T. Wang and T. Hwang, "Through-Silicon Via Planning in 3-D Floorplanning," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 19, no. 8, pp. 1448-1457, Aug. 2011,

- [10] C. Li, W. Mak and T. Wang, "Fast Fixed-Outline 3-D IC Floorplanning With TSV Co-Placement," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 21, no. 3, pp. 523-532, 2013.

- [11] Sivaranjani, P., Senthil Kumar, "A. Thermal-Aware Non-slicing VLSI Floorplanning Using a Smart Decision-Making PSO-GA Based Hybrid Algorithm," *Circuits Syst Signal Process* vol. 34, pp. 3521–3542, 2015

- [12] Atul Prakash & R. K. Lal, "Floorplanning for Area Optimization Using Parallel Particle Swarm Optimization and Sequence Pair," in *Wireless Personal Communication*, vol. 118, pp. 323-342, 2021.

- [13] Sadiq M. Sait, Feras Chikh Oughali, Mohammed Al-Asli, "Design partitioning and layer assignment for 3D integrated circuits using tabu search and simulated annealing," *Journal of Applied Research and Technology*, Volume 14, Issue 1, pp. 67-76, 2016.

- [14] M. E. Ekpanyapong and S. K. Lim, "Simultaneous delay and power optimization for multi-level partitioning and floorplanning with retiming," in Proc. *the Int. Symp. on Circuits and Systems (ISCAS 2004)*, Vancouver, Canada, pp. 1-9, May 2003.

- [15] MCNC/GSRC Benchmark, Retrieved from <a href="http://vlsicad.cs.binghamton.edu/benchmarks.html">http://vlsicad.cs.binghamton.edu/benchmarks.html</a>.